RETURN TO ARK L. LEW

Operator Manual for the RCA COSMAC Development System II CDP18S005

**MPM-216**

Suggested Price \$10.00

**Operator Manual** for the RCA COSMAC **Development System II** CDP18S005

Information furnished by RCA is believed to be accurate and reliable. However, no responsibility is assumed by RCA for its use; nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of RCA.

Trademark(s) Registered ® Marca(s) Registrada(s)

Copyright 1977 by RCA Corporation (All rights reserved under Pan-American Copyright Convention)

### **Foreword**

The COSMAC Development System CDP18S005 is a prototyping aid for the design of hardware and software systems based on the RCA CDP1802 microprocessor. The COSMAC Development System is specially structured to provide a testbed in which hardware/software prototypes of systems containing a microprocessor may be designed, built, and tested. In small-volume applications it can be used as the major building block for dedicated microcomputers.

This Manual is designed as a guide for the COSMAC Development System user. It includes a detailed description of each of the available hardware modules as well as a complete explanation of the functions available from the software sup-

plied with the system.

The COSMAC Development System (CDS) consists of a card nest with self-contained power supply, an easy-to-use control panel, and a basic set of plug-in modules. It is packaged to promote easy interfacing with external devices. These interfaces may be custom-designed by the user or, in the case of common peripheral devices, are available from RCA as standard optional modules, and include a floppy disk interface.

The COSMAC Resident Software Package (which runs on the CDS in a stand-alone manner) provides a means for rapid coding and debugging of COSMAC programs. Many of its features are compatible with those of the COSMAC Software Development Package (CSDP) timesharing program-development aids. Additional software and firmware packages are available from RCA including packages for floppy disk hardware and multiple precision arithmetic.

## **Table of Contents**

|                                                                    |          |            |     |             |       |             |     |      |       |      |     |      |     | Page |

|--------------------------------------------------------------------|----------|------------|-----|-------------|-------|-------------|-----|------|-------|------|-----|------|-----|------|

| Foreword                                                           |          |            |     | •8          | •     | ): <u>•</u> |     | *    |       | ; (• |     |      | •); | .3   |

| Operating and Programming the CDS                                  | •        |            |     | <b>2</b> 5  |       | 22          |     |      | n 😭   | 24   |     | ¥    | 25  | 9    |

| System Overview                                                    |          |            |     | *0          | 300   |             |     |      |       | 106  | į.  | *    | *** | 9.   |

| Initial Operation                                                  |          |            |     | *9          | ((4)) |             |     |      |       |      |     | ¥    |     | 10   |

| CDS Hookups                                                        |          |            |     | •0          |       | 92          |     | •3   |       | 7    |     |      | . 2 | 10   |

| CDS Checkout Program                                               |          |            |     | 10          |       |             |     | 27   | V-2   |      |     |      | 3   | 10   |

| Loading and Outbutting Programs                                    |          |            |     | 40          | 9.00  | 91          | 1.5 | 20   | 7/20  |      | 100 | - 53 | 20  | 11   |

| Paper Tape Systems                                                 |          |            |     |             | 30    |             | 8   |      |       |      |     |      |     | 11   |

| Paper Tape Systems                                                 |          |            |     | •           |       |             |     |      | •     |      |     |      |     | 11   |

| Introduction to the Monitor Software UT:                           | 20       |            |     | •           |       |             |     |      |       |      |     |      | •   | 12   |

| Utility Commands                                                   |          |            |     | • 6         |       |             |     | *    | 0(*0) | 0.   |     |      | •5: | 12   |

| ?M Commands                                                        |          |            |     | •           | 300   | *           | æ   | *    |       | 9    | 9   |      | •   | 12   |

| !M Commands                                                        |          |            |     | <b>\$</b> 2 |       | 24          | *   |      |       |      |     |      | 40  | 12   |

| \$U Commands                                                       |          |            |     |             |       |             | 2   | 4    |       | 9    |     |      |     | 13   |

| \$P Commands                                                       |          |            |     |             | (*)   |             |     |      |       |      |     |      |     | 13   |

| \$L Commands                                                       |          |            |     |             |       |             |     |      |       |      |     |      |     | 13   |

| ?R Commands                                                        |          |            |     | •0          | 0.00  | 2.          | *   | **   |       |      |     | •    | •   | 13   |

| Summary of UT20 Operating Instruction                              |          |            |     |             |       |             |     |      |       |      |     |      |     |      |

| Terminal Interfacing                                               |          |            |     |             | 0.00  | V.          |     |      |       |      |     |      |     | 15   |

| ASCII Coding                                                       |          |            |     | 100         | 200   | 82          | 92  | 9    | W.    | 547  |     |      | 20  | 15   |

| UT20 Read and Type Routines                                        |          |            |     | 20          | 520   | (2          |     |      |       |      | -   |      | 10  | 15   |

| Examples of UT20 Read and Type Usas                                | re e     |            |     | - 8         | 150   | 16          | 8   | 2    |       |      | Ů.  | *    | 20  | 18   |

| Examples of UT20 Read and Type Usag<br>Additional Utility Routines | <b>-</b> | •          |     | 5.1         | 1,00  | (17         | .0  | - 2  |       |      | 75  |      | 70  | 19   |

| ASCII to Hex Conversion Routine                                    |          | •          |     | 70          | 0.50  | 0.5         | 15  | - 27 | 1 71  | 8    | 1.5 | - 01 |     | 19   |

| Initialization Routines                                            |          |            |     |             |       |             |     |      |       |      |     |      |     | 19   |

| Routine to Restart UT20                                            |          |            |     |             |       |             |     |      |       |      |     |      |     |      |

| Additional Notes on UT20                                           |          |            |     |             |       |             |     |      |       |      |     |      |     |      |

| Programming Methods                                                | •        | •          |     | •           | 1.0   | 15          |     | •    | •     | *    | •   | •    |     | 20   |

| Machine Language Programming                                       | •        | ٠,         |     | 50          |       | 11.         |     |      | Ē/i   | .*/  | *   |      | *   |      |

| Programming Interface to CSDP                                      | •        | •          |     |             | 9.5   | 67          | 11  | 31   | •8    | .*.  | S.  |      | .5  | 22   |

|                                                                    |          |            |     |             |       |             |     |      |       |      |     |      |     |      |

| Hardware Structure of the CDS                                      |          |            |     |             |       |             |     |      |       |      |     |      | 2   | 27   |

| System Block Diagram                                               |          |            |     |             |       |             |     | (4)  | 27    |      | 24  |      | 8:  | 27   |

| Module Description and Signal Mnemonics                            | s.       |            |     |             |       |             | 12  |      | 20    |      | 7.0 | 12   | ¥.  | 29   |

| Card Nest and Backplane                                            |          |            |     |             |       |             |     |      |       | •    |     |      |     | 29   |

| CDU Madula CDD19C102                                               |          |            |     |             |       |             |     |      |       |      |     |      |     | 30   |

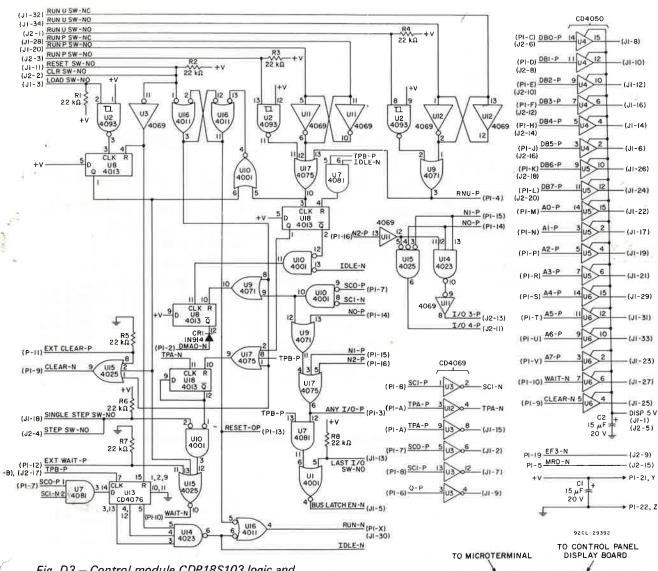

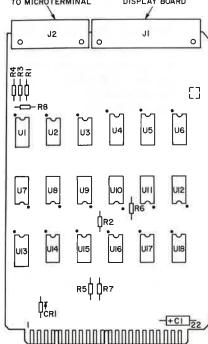

| Control Module CDP18S103                                           |          |            |     |             | •     | 5.0         |     |      | •2    |      |     |      |     | 31   |

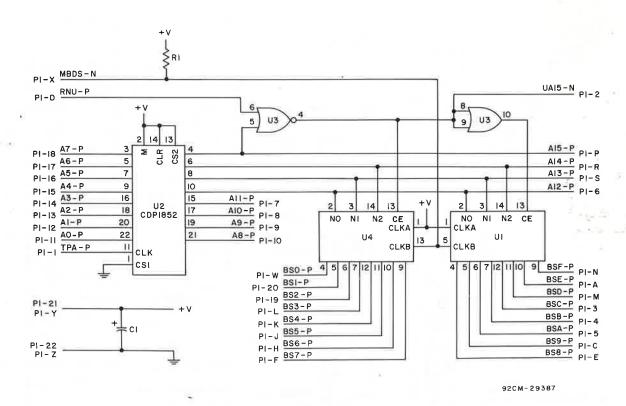

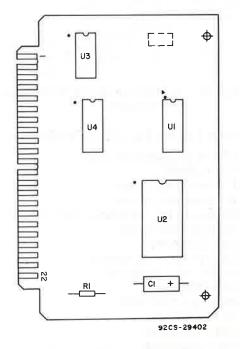

| Address Latch and Bank Select Module (                             | CDP1     | <b>8</b> S | 206 |             | •     |             |     |      | •8    | 1.00 | 8   |      |     | 32   |

| I/O Decode Module CDP18S509                                        |          |            |     | *           | *0    | 5000        | 24  |      | •     | 0.00 | 396 | ik.  |     | 33   |

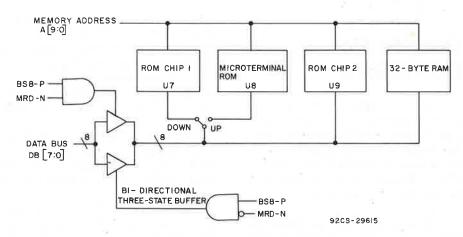

| ROM/RAM Module CDP18S401                                           |          |            |     |             | 40    | •           | 32  |      | 20    |      |     |      |     | 34   |

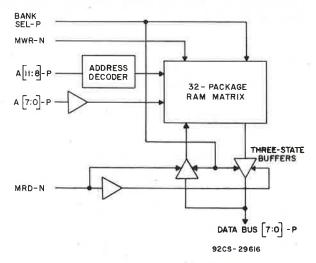

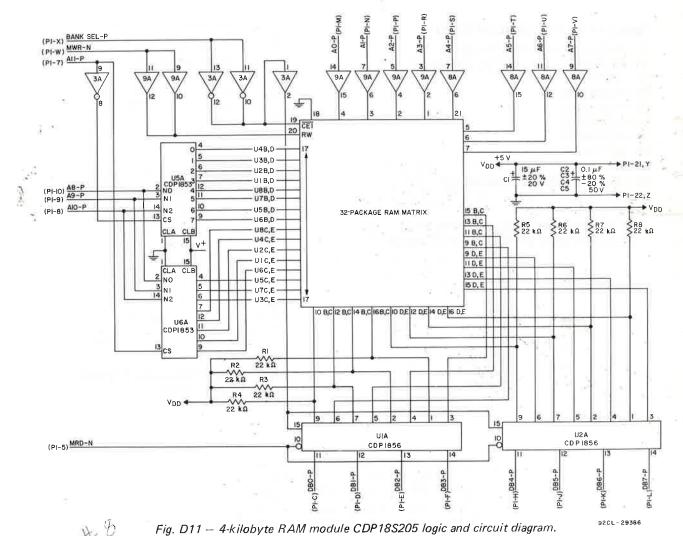

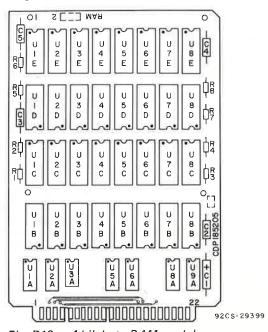

| 4-Kilobyte RAM Module CDP18S205 .                                  |          |            |     | -           | 20    | •           |     | ٠    |       | 30   | 114 |      |     | 34   |

| Control Module CDP18S102                                           |          | 12         |     |             |       | 0.0         |     |      |       | 60   |     |      | 2   | 35   |

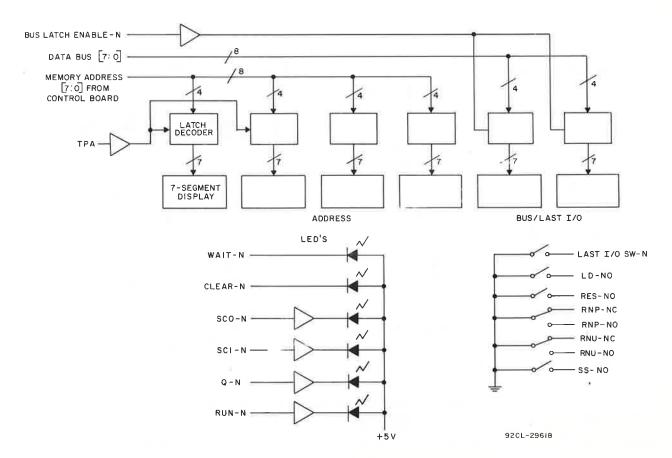

| Display Board                                                      |          |            |     | Ţ           |       |             |     |      |       |      |     |      | 8   | 36   |

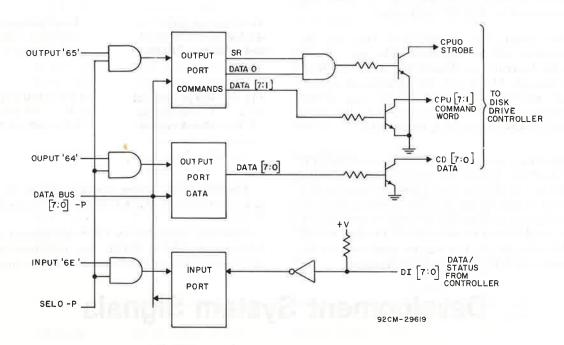

| Disk Interface Module Option CDP18S8                               | 13       |            |     |             | •     |             | 2.  |      |       | 1.40 |     |      |     | 37   |

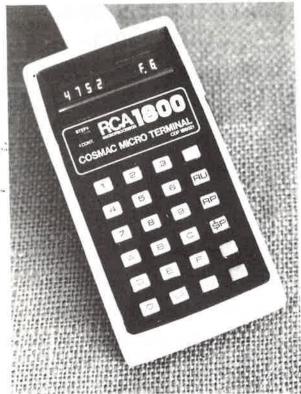

| Microterminal Option CDP18S021                                     |          |            |     |             | **    | 1.07        | 794 |      |       |      |     |      |     | 37   |

| Display Board                                                      |          |            |     |             | +3    |             | 0.  |      | *     |      |     |      |     | 38   |

|                                                              |          |      |      |      |     |      |      |         |        |      |            |              |      |     |               |            | Page |

|--------------------------------------------------------------|----------|------|------|------|-----|------|------|---------|--------|------|------------|--------------|------|-----|---------------|------------|------|

|                                                              |          |      |      |      |     |      |      |         |        |      |            |              |      |     |               |            | 38   |

| Development System Signals                                   | •        | •    | •    | •    | •   | •    | •    | •       | *      | 35   | *          | •            | ٠    | 9.5 | å _           | 7.         | 40   |

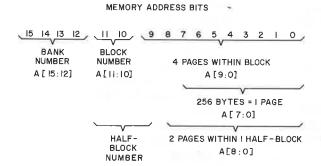

| Memory Addressing and Expansion                              | •        | •    | •    | •    | •   | ٠,   |      | •       | 90     |      | •          | •            | (•€  |     | ÷             | *          | 40   |

| Memory Organization                                          | ٠        | ٠    | •    | •    | •   | •    | •    | •       | •      | •    | •          | •            | •    | 90  | *             | *          | 40   |

| RCA Modules                                                  |          | •    | •    | •    | •   | •    | •    |         |        |      |            | *            | •    | •   | *             | ٠          | 41   |

| Custom Memory Modules                                        | •        | •    | •    |      |     | •    | •    |         | •      | •    | •          | •            | *    | •   | •             |            | 41   |

| Input/Output Interfacing                                     | •        |      | •    | •    | •   | •    | •    | •       | •      |      | •          | •            |      |     | •             | •          | 42   |

| Module Enable Philosophy                                     |          |      |      | •    | •   | •    | ٠    | •       | 1:0    | (9)  | ÷          | •            | •    | •   | •             | •          | 42   |

| Two-Level I/O                                                |          | :    |      | •    | •   | •    | •    | ٠       | *3     | •    | ě          |              | 53   |     |               | *          | 42   |

| Interfacing Signals and Custom I/O                           | Mo       | odu  | les  | •    | •   |      | •    | •       | *      |      |            | 90           | *:   | (*) | 5 <b>.</b>    | •          | 45   |

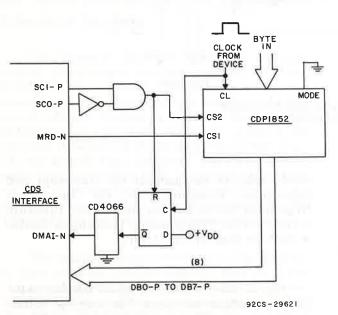

| DMA Input                                                    |          |      | •    | •    | •   | ٠    | •    | •       | •2     |      |            | ٠            | *    | (•) | 2.0           |            | 45   |

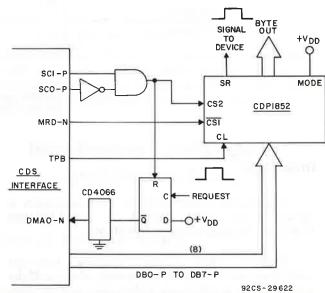

| DMA Output                                                   |          |      |      |      |     |      |      |         | -      |      |            | 4            | (4)  | 00  | ₹9            | *          |      |

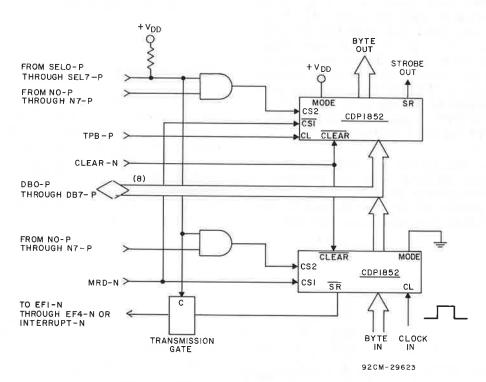

| Byte I/O                                                     |          |      | •    | •    |     |      |      | •       | •      | •    | •          | ٠            | •    |     | 4             | æ          | 46   |

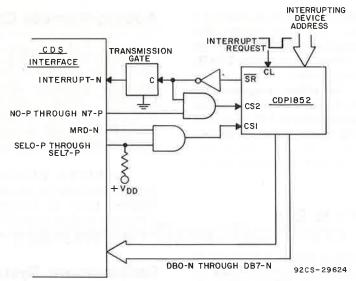

| Interrupt                                                    |          |      |      |      | ٠.  | :    |      | •       | •      |      | •          |              | •    | •   | •             |            | 46   |

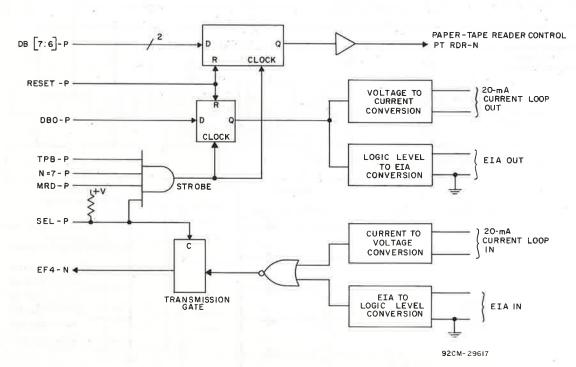

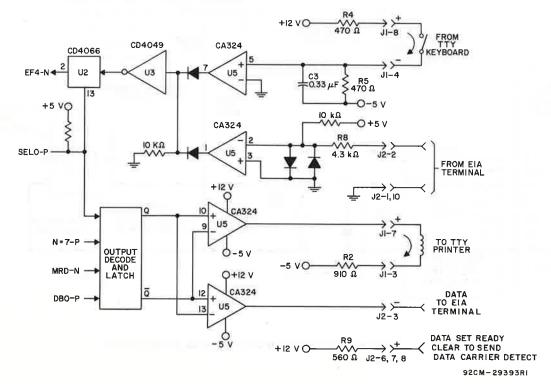

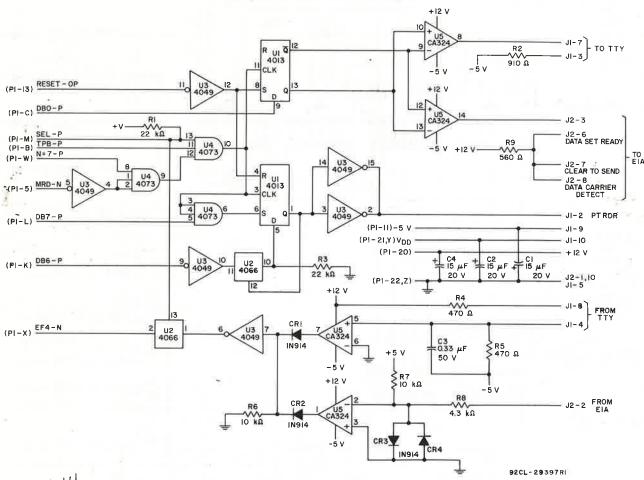

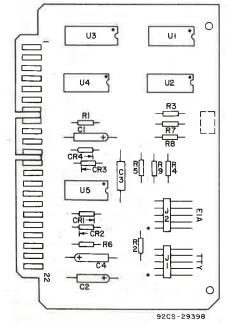

| Bit Serial Interface—The Terminal                            | In       | terf | ace  | Mo   | odu | ıle  |      | •       | *:     | ٠    | . <b>.</b> | : <b>*</b> : |      | •   | •             |            | 47   |

| Interfacing Techniques and Precaut                           | ion      | ıś   |      |      |     | •    |      | •       | *(     | •0   |            |              | *    | 16  | \$ <b>•</b> 8 | 2.         | 47   |

| Use of External Clock                                        |          |      |      |      |     |      |      |         | (4)    | *3   |            | <b>(</b>     |      | • 2 | 0.07          |            | 4/   |

| External Flags EF1 to EF4                                    |          |      |      |      |     |      |      |         | Ŧ      | \$5  | •          | 22           | ä    | •   | 0,00          | •          | 48   |

| Adding I/O Devices                                           |          |      |      |      |     |      |      |         |        | •    |            | ÷.           |      | *   |               | <b>6</b> 5 | 48   |

| Adding I/O Devices Adding Remote Control                     |          |      |      |      |     |      |      |         | ž      | •    | ٠          | ě            |      |     | 1             | 74         | 48   |

| Dovolonment System Dynamic Ch                                | ara      | acte | rist | ics. |     |      | _    |         |        |      |            |              | 4    |     |               | 2.0        | 40   |

| Troubleshooting                                              |          |      |      |      |     |      |      |         | 99     | *:   | ×.         |              | 8    | •   | •             | •          | 48   |

| Hardware Specifications                                      |          |      |      |      |     |      |      |         | ).e    |      | •0         |              | 28   | •   | *6            | •          | 49   |

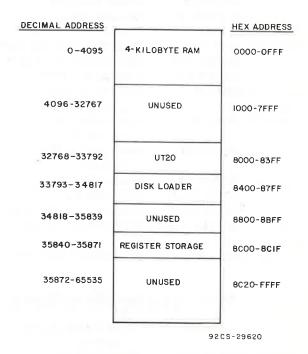

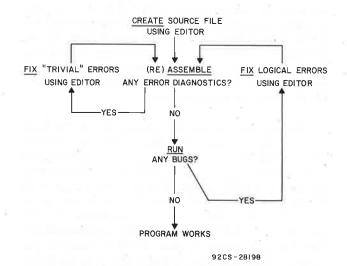

| CDS Resident Software Development                            | Λi       | de   |      |      |     |      |      |         |        |      |            | 200          | 02   |     | 2.            |            | 51   |

| CDS I/O Terminals                                            | Л        | us   | •    | •    | •   | •    | •    | •       | ©<br>∞ | 3    |            | 0.0          |      |     |               |            | 51   |

| Mamaru Space Paguirements                                    | ٠        | •    | •    | •    | •   | •    |      | •       |        | 8    | 8          |              | ā    |     | ¥.            | 8          | 51   |

| Memory Space Requirements Informal Introduction to the COSM. | ٠<br>۵ د | Re   | side | nt   | Δς  | sen  | nhla | ·<br>er | 95     | , a  |            |              | ÷.   | 0   |               | 2          | 52   |

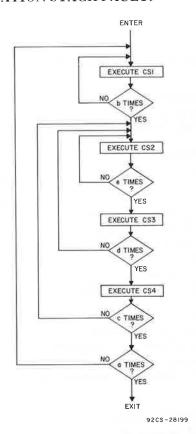

| Flow Chart to Operation Mnemonic                             | rc<br>Cs | 1    | siuc | /11t | 113 | 3011 | 101  | -       | 10.5   | •    | •          |              |      |     | 3             | 3          | 52   |

| Addressing                                                   | Ç3       | •    | •    | •    | •   | •    | •    | •       |        |      |            | 10           | 27.0 |     | 7.            |            | 53   |

| Assembly Language Equivalent                                 | •        | •    | •    | •    | •   | •    | •    | •       |        |      |            |              | 100  | 10  | .0            |            |      |

| COSMAC Resident Assembler                                    | •        | •    | •    | •    | •   | •    | •    | •       | 220    | Ċ    | į.         | 20           | 000  | 5.0 |               | *          |      |

| Assembler Operation                                          | •        | •    | •    | •    | •   | •    | •    | •       |        |      |            |              | 540  | Ž.  | -             |            | 54   |

| The Location Counter                                         | •        | •    | •    | •    | •   | •    | •    | •       | 500    | 2    | Ž.         |              | 100  | 82  |               | ٠          | 55   |

| The Symbol Table                                             | •        | •    | •    | •    | •   | •    | •    | •       |        | Č.   | 8          | 20<br>10     |      | 1   |               |            | 55   |

| Expression Evaluation                                        | •        | •    | •    | •    | •   | •    | •    | •       |        | 7.   | ·          | - 2          |      |     | - 2           |            | 55   |

| COSMAC Level I Assembly Langua                               | and      | •    | •    |      | •   | •    | •    | •       |        | 37   |            |              |      |     |               | -81        | 55   |

| Lines and Comments                                           | igc      | •    | •    | •    | •   | ٠    | •    | •       | 11.00  |      | 1.5        |              | 20   |     | - 2           | -          | 55   |

| Symbol Definitions                                           | •        | •    | •    | •    | •   | •    | •    | •       | 10.0   |      |            |              |      |     |               |            | 56   |

| Explicit Constants                                           | •        | •    | •    | •    | •   | •    | •    | •       |        | 000  |            | į            | 20   | 200 | 02            |            | 56   |

| Address Constants                                            | •        | •    | •    | •    | •   | •    | •    | •       | -      | 50   |            |              | 30   |     | 74            |            | 57   |

| Operation Mnemonics                                          |          |      |      |      |     |      |      |         |        |      |            |              |      |     |               | 00         | 57   |

| Instructions and Operands                                    | •        | •    | ٠    | •    | •   | •    | •    | •       | *0     | •    | •          | Ť            |      |     | 21            | 85         | 57   |

| Data Lists                                                   | •        | •    | •    | •    | •   | •    | •    | •       | • 2    | 0.82 | 1.0        |              | •    | •   |               | - 25       | 58   |

| CRA Directives                                               | •        | •    | •    | •    | •   | •    | •    | •       |        |      |            | •            |      | *2  | 0.0           |            | 58   |

| CRA Directives                                               | •        | •    | •    | •    | •   | •    | •    | ٠       |        |      |            |              |      |     |               |            | 58   |

| Additional Notes                                             | •        | •    | •    | •    | •   | •    | •    | •       | •      | •    | (*)        | •            | Ů    | •   |               | •          | 59   |

| Code Examples and Review                                     | •        | •    | •    | ٠    | •   | •    | •    | •       | Ž.     | 7/.  | ٠          |              | •    | •   | (0)           |            | 59   |

| Error Messages                                               | •        | •    | •    | •    | •   | •    | •    | •       |        | •    |            | 3.5<br>On    | 8    | *   | 11.           | •          | 63   |

| Code Examples and Review                                     | •        | •    | •    | •    | •   |      | •    | •       | •      | •    |            |              | .*   | **  |               | •          | 63   |

| Summary of CRA Operating Step                                | S        | •    | •    | ٠    | ٠   | ٠    | ٠    | ٠       | ٠      | •    | 0.00       | ::#          | :*   | *   | •             | \*/        | 64   |

| RAM Considerations                                           |          |      | •    | ٠    | ٠   | ٠    | ٠    | •       | ٠      | •    | 116        |              | •    | (4) | •             | 7.0        | 64   |

| Output Options                                               | •        | •    | •    | ٠    | •   | •    | •    | ٠       | •      |      | •          | •            |      |     | 15            | •          | 64   |

| Prompt Messages                                              |          |      |      |      | •   | ٠    | •    | •       |        | •    | •          | •            |      | •   | •             | •          | 04   |

|                                                                  |            |                  |         | Page |

|------------------------------------------------------------------|------------|------------------|---------|------|

| Informal Introduction to the COSMAC Resident Editor              |            |                  |         | 65   |

| COSMAC Resident Editor                                           | •          | 20. 9            |         | 66   |

| CRE Operating Considerations                                     | •          | 900 0            |         | 66   |

| Memory Space Requirements                                        | •          | <b>(8</b> ) 9    | * *     | 66   |

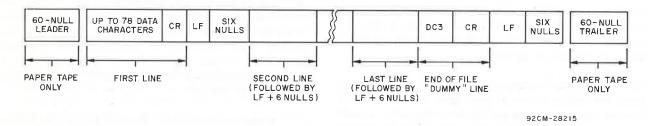

| Input and Output Files                                           | *          | :00 G            |         | 66   |

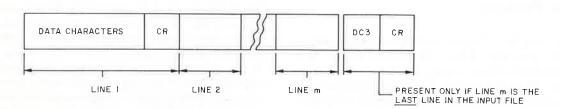

| Record Formats                                                   | ¥0 - 1     | Ø€ - 9           |         | 66   |

| Buffer Pointer                                                   | ¥8         | ·                |         | 68   |

| CRE Command Operation                                            |            | 1                |         | 69   |

| Command Strings                                                  | •          | <b>(6)</b>       |         | 69   |

| Command Formats                                                  | •          | •                |         | 69   |

| Punch Procedure                                                  | <u>16</u>  | sta s            |         | 70   |

| Correcting Command Typing Errors                                 | *:         | <b>.</b>         | 4. 8    | 70   |

| Interrupting CRE Execution                                       | <b>y</b> : | ( <b>#</b> E = E |         | 70   |

| Filled Work Space Warning                                        |            |                  |         |      |

| CRE Commands                                                     |            | 1 <b>5</b> 2 8   | *8 9    | 70   |

| Single Commands                                                  |            |                  |         |      |

| Pointer Control Commands                                         | *          |                  |         | 71   |

| Reading the Input Tape                                           | *          | · .              |         | 71   |

| Deletion Commands                                                | 2          |                  | ÷7. 3   | 71   |

| Text Insertion and Data Manipulation                             |            |                  |         | 71   |

| Output Commands                                                  |            |                  |         | 72   |

| Summary of CRE Commands and Control Characters                   |            | <b>1</b> 0       |         | 72   |

| Composite Commands and Nesting                                   | *          | n s              | · .     | 72   |

| Horizontal Tabs                                                  | *          | <b>€</b> 1 8     | 90) 54  | 74   |

| Additional Note                                                  | *          | <b>€</b> 8 9     | ¥0 0¥   | 74   |

| Using CRE                                                        | ÷          | £ 8              | e _ 2•  | 75   |

| Loading and Operating CRE                                        |            | <b>8</b> 8       |         | 75   |

| File Development and Manipulation                                |            | \$ Z             |         | 75   |

| Creating a File                                                  |            | <b>*</b> : 1     |         | 75   |

| Adding to a File                                                 |            | •8 8             |         | 75   |

| Deleting a Section in a File                                     |            | *0 (6            | *: 0*   | 76   |

| Moving a Section in a File                                       |            | <b>2</b> ( )     | 96 S4   | 76   |

| Modifying a Section in a File                                    |            | ¥0 0             | a 4     | 76   |

| Modifying a Section in a File                                    |            |                  |         | 77   |

|                                                                  |            |                  |         | 79   |

| ppendices                                                        |            |                  | *       |      |

| A. CDS 18S005 Backplane Wiring Schedule                          | ė          | <b>5</b> 8 3     | • •     | 79   |

| B. Instructions for Converting a Model 33 Teletype Terminal from |            |                  |         |      |

| Half-to-Full-Duplex Operation and from 60-mA to 20-mA Operation  | •          | <b>8</b> 2 - 3   | F 3     | 81   |

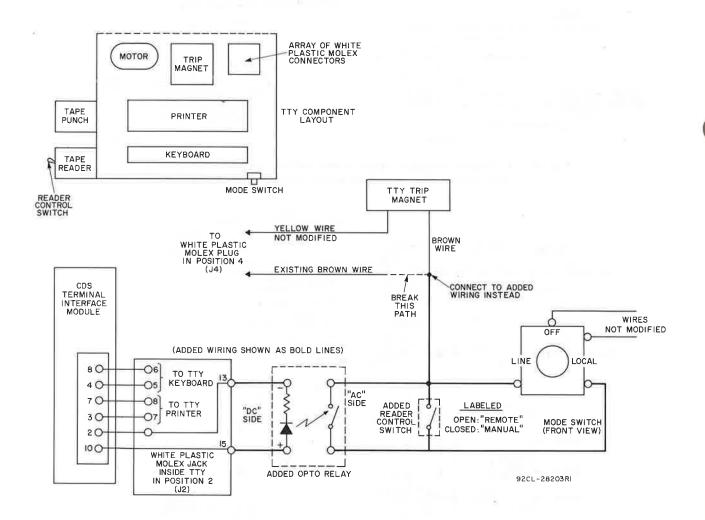

| C. Adding Teletype Remote Reader Control                         | ÷          | 8                |         | 82   |

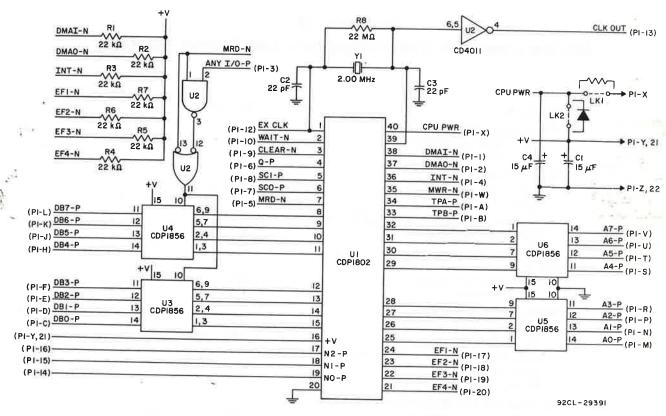

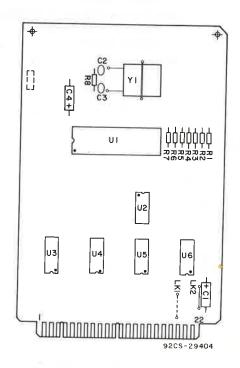

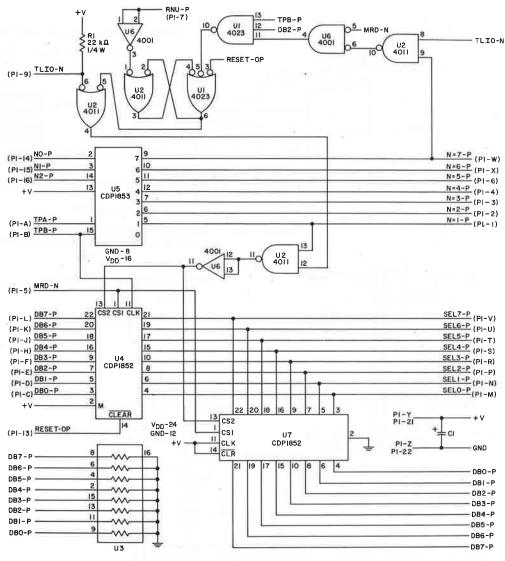

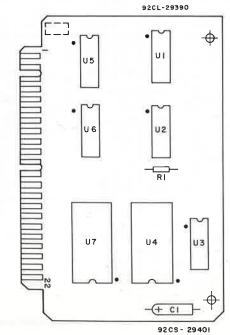

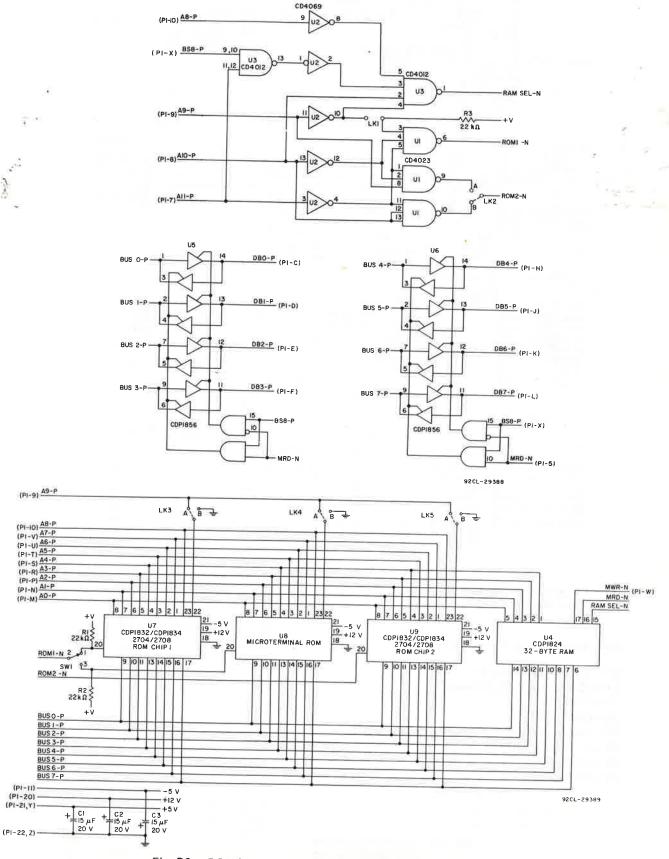

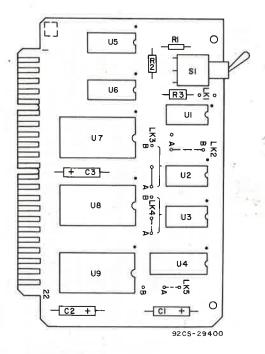

| D. Module Logic and Circuit Diagrams and Layout Diagrams         |            | 9                |         | 83   |

| E. Instruction Summary for RCA CDP1802 COSMAC Microprocessor.    |            |                  |         | 95   |

| F. ASCII – Hex Table                                             |            | 83               |         | 99   |

| G. UT20 Listing                                                  | )•         | ·                |         | 100  |

| H. System Checkout Game – DEDUCE                                 | ×          | *                | ic (ii) | 121  |

| I. Conversion to Different Operating Voltages                    |            | 25               |         | 123  |

| I Connection List for Terminal Interface Cables                  | 8          |                  | 20 020  | 123  |

# Operating and Programming the CDS

# **System Overview**

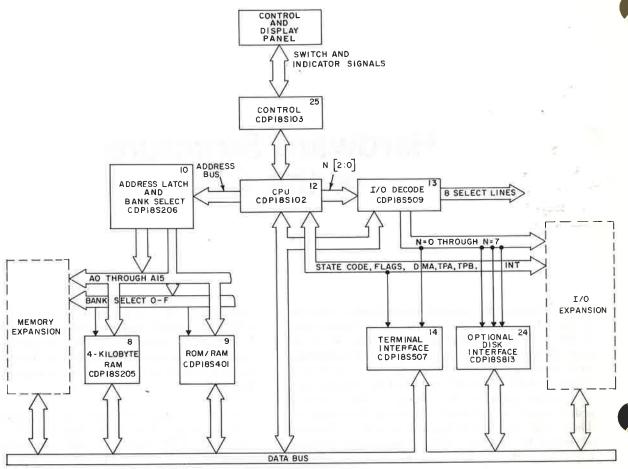

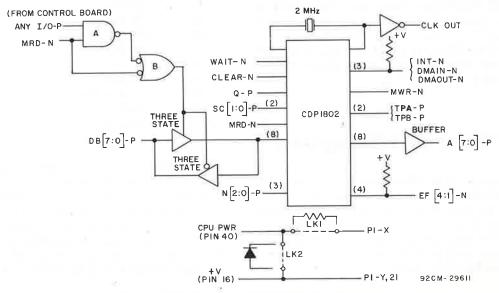

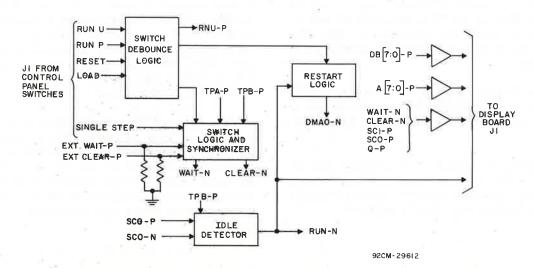

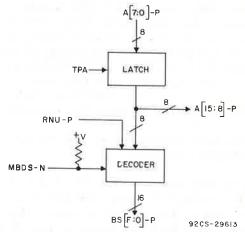

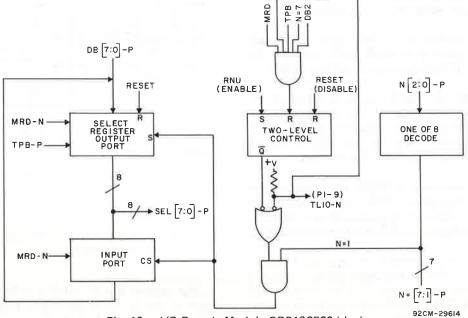

The CDP18S005 COSMAC Development System (CDS) consists of a power supply, control panel, and a set of connectors for printed circuit boards. Many of the 25 available positions are occupied by specific module types. A printed circuit backplane distributes common signal lines to all connector positions. There are a small number of additional wire-wrapped connections. The unassigned connectors are available for user expansion of memory and I/O function.

Supplied modules include the CDP1802 CPU module, an address latch and memory bank select module, a 4-kilobyte RAM module, a ROM/RAM module containing the Utility program, an I/O decode module, terminal interface module, and a control module. The position assignments of these modules are given in Table III in the next Section. All logic functions are implemented in CMOS operating at  $\pm$  5 V.

The control panel provides a simple user interface. Depressing the RESET switch initializes the system. Depressing the RUNU switch starts the utility program, identified as UT20. Depressing RUNP, on the other hand, will start program execution from memory location 0, the normal starting location of a user program. A STEP/CONTINUOUS switch allows stepping one machine cycle with each depression of RUNU or RUNP. A 4-digit display on the front panel shows the current address and a 2digit display shows the value of the data bus or, by switch selection, the last I/O data byte. Five additional LED indicators monitor the State Code, WAIT, CLEAR, and Q lines of the CPU while a sixth LED indicates when the machine is running. This RUN indicator will be ON whenever the CPU is running and not in the IDLE mode. The LOAD switch is used to place the CPU in the 'load mode' in which the DMA channel can be used to load RAM.

See The User Manual for the CDP1802 COSMAC Microprocessor, MPM-201, for a detailed discussion of this mode. The LOAD switch is supplied as a convenience for the user designing his own system interfaces and is not used in normal CDS operations. The supplied programs are loaded using the Monitor program as discussed in the next section.

The CDS is designed to work with any one of the following terminals:

- 1) An ASR 33 Teletype terminal (or its electrical equivalent) which should include a remote reader control circuit to permit the CDS to control the paper tape reader.

- 2) A TI "Silent 700" terminal, Model 733 ASR with tape cassettes and "Remote Device Control" option. This terminal uses dual program-controlled magnetic tape cartridges as storage medium and prints at 30 characters per seconds.

- 3) Any terminal conforming to the EIA RS232C standard interface and having a baud rate of 110, 300, or 1200.

The CDS is designed to automatically adjust to a variety of data terminal speeds and will accommodate either full- or half-duplex operation.

Included with the CDS are an assembler and editor program for software development. Loading instructions for these programs are given in the next subsection. Details on operation of the Assembler and Editor are given later in this manual. If a Floppy Disk system is used with the CDS, refer to the Floppy Disk Manual for operation of the Assembler, Editor, and other programs.

Registered Trademark, Teletype Corporation.

A Registered Trademark, Texas Instruments Corporation.

# **Initial Operation**

## **CDS Hookups**

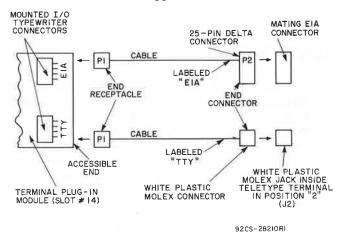

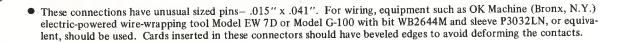

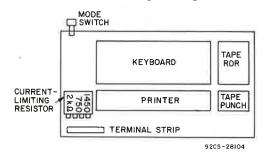

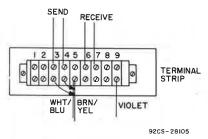

Two I/O data terminal cables are supplied with the Development System - one for terminals using a 20-mA loop interface, the other for an EIA RS232C data terminal. Each cable with its terminal board connection is labeled. To connect the data terminal, select the proper cable and plug its receptacle labeled "P1" into the appropriate connector mounted directly on the accessible end of the terminal board, as shown in Fig. 1. For a list of terminal interface cables and their functions, refer to Appendix J.

Fig. 1 — Cable connection for I/O data terminals.

The two connectors on the terminal board are labeled appropriately. The connector on the other end of the cable plugs into the terminal. For a Teletype terminal, remove its cover and plug the cable into connector position 2 (J2) in the array of white plastic Molex connectors located in the back of the unit. For an EIA terminal, plug the EIA connector on the cable into the receptacle on the back of the data terminal. Fig. 1 shows these connections.

When the Silent 700 terminal is used, the cable supplied with that device should be connected to the CDS via the EIA cable.

Put the terminal in the Line mode, select the appropriate baud rate and set for full-duplex operation before attempting to use any terminal.

Appendix B gives instructions for converting a TTY from half- to full-duplex operation. The interface is a 20-mA current loop. Make necessary changes per Appendix B to convert a TTY to 20-mA operation. If a TTY is to be used with the assembler program, the remote reader control circuit should be installed in accordance with the instructions in Appendix C. Once installed, its switch should be set in the MANUAL position before continuing.

Install the power cable and switch power on. Press RESET followed by RUNU. This sequence will cause the RUN light to go ON and the system is now operating with UT20 in control.

This program begins by reading the first keyboard input character to define for itself the terminal character rate and whether it should "echo" typed information to the data terminal printer. If the terminal is operating in the full-duplex mode, the user should begin by pressing the RETURN key on the keyboard. For the half-duplex mode, the user should press the LINE FEED key instead. The system then responds with the prompt character (\*). It now "knows" the essential characteristics of the I/O data terminal. Reaching this stage verifies that most of the hardware is operating properly.

## **CDS Checkout Program**

Even with little or no knowledge of the COSMAC command repertoire, the user can further verify proper system operation by loading, from the terminal, an elementary test program. For example, a simple time-out loop can be run in which the RUN light goes off after a specific elapsed time from the initiation of execution.

Each line of user keyboard input is terminated by a depression of the RETURN key on the keyboard. The test time-out program can be loaded into memory by typing in

#### !M0 △F8FFB1219191913A0300(CR)

The system will reply with the prompt character. One can verify proper loading by entering

#### $?M0\triangle A(CR)$

The system will print the characters just entered (after the memory location addressed, "0000" in this case) and will return the prompt character again. The time-out program can then be run either by entering

#### \$P0(CR)

or by depressing RESET followed by RUN. In either case, the RUN indicator should go off after approximately 2.6 seconds. This step establishes that the read-write memory (RAM) is operational.

• In this Manual, (CR) at the end of an example of a user keyboard input denotes the terminating carriage RETURN. Spaces in an input line will be denoted by blanks in the example or, for additional emphasis, by the symbol  $\Delta$

# Loading and Outputting Programs

Programs may be entered manually by use of the !M command, just described. This and other Monitor commands are covered in detail in the next section. Ordinarily, programs will be loaded from paper tape via a TTY, from magnetic tape cassettes via the TI terminal, or from a floppy diskette via the Floppy Disk system. The latter is covered separately in the RCA COSMAC Floppy Disk System CD-P18S805 Instruction Manual MPM-217. RCA-supplied CDS programs are designed to work in the full-duplex mode.

Following are the methods used with paper tape and magnetic cartridges:

### **Paper Tape Systems**

To load a paper tape:

- 1) Press RESET, followed by RUN U.

- 2) Press the RETURN key (CR) on the TTY. Make sure it is in the LINE Mode and the installed switch is in the MANUAL position.

- 3) UT20 will return the symbol \* indicating it is ready to accept commands.

- 4) Position the tape in the header and turn on the tape recorder.

- 5) When loading is complete, UT20 will issue another \*.

- 6) Start the program by typing \$U0(CR).

If preferred, typing can be suppressed during paper-tape loading by pressing the LINE FEED key instead of CR at step 2. In this case, the user should re-initialize the system after loading by pressing RESET, RUN U, and CR before attempting to start the loaded program.

UT20 monitors the program being loaded and will issue a ? if a format error is detected. If an error is detected, stop and reload the tape from the beginning.

To punch reloadable tape:

1) With the TTY in the LOCAL mode, position tape in the punch, turn the punch ON, and make a header of nulls (control-shift-P).

- 2) Type !Maaaa  $\triangle$  where aaaa is the hex address of where the data is to be reloaded (normally location 0000).

- 3) Turn the punch OFF and put the TTY in the LINE mode.

- 4) Initialize the CDS with a RESET, RUNU, followed by a RETURN (CR).

- 5) Next, type ?Maaaa \( \triangle \) count, where the address is the starting address of data to be read from memory, and count is the number of hex bytes to be punched.

- 6) Turn the punch ON and press CR. After the tape is punched, some more nulls should be added to its end.

The assembler and editor programs automatically punch reloadable tape as described in the Section titled CDS Resident Software Development Aids.

### **Magnetic Tape Systems**

To load a magnetic tape:

- 1) Press RESET, RUN U, then CR.

- 2) UT20 will return the symbol \*.

- 3) Mount the cassette. Rewind it and press LOAD/FF to advance to the first record. Make sure the drive is in the LINE and PLAYBACK mode.

- 4) When loading is completed, UT20 will issue another \*. Start the program by typing \$U0(CR).

Typing during load can be suppressed by turning the printer OFF. If a ? is typed during loading, an error has been detected and the tape should be reloaded.

To record reloadable tape:

- 1) With the terminal in the LOCAL and RECORD mode, mount a blank cartridge.

- 2) Type !Maaaa \( \Delta\) where aaaa is the hex address of where data is to be reloaded (normally location 0000).

- 3) Switch to the LINE and PLAYBACK mode and initialize the CDS with a RESET, RUN U, and CR.

4) Type ?Maaaa △count, where the address is the starting address of the data to be read from memory and count is the number of hex bytes to be recorded.

5) Turn the Record Control switch ON and press CR. After the data has been output, UT20 will issue another \*.

For another system checkout program using the supplied "Deduce" game, refer to Appendix H.

# Introduction to the Monitor Software UT20

## **Utility Commands**

The CDP18S005 COSMAC Development System includes a Monitor program, known as UT20, which performs commonly required functions of running the terminal interface, providing a means of reading and generating reloadable tape, giving access to all memory locations, and allows the user to start program at a given location. The following explains in detail the ?M and !M commands already mentioned, plus others not yet discussed.

In general, after the system has been RESET, the user has two choices: pressing RUN begins execution of his program at location 0000, while pressing RUN U begins execution of UT20 (at 8000). After pressing RUN U, the user next presses either a LF (line feed) or a CR (carriage return) key, depending upon his installation. A CR initiates FULL DUPLEX operation, an LF, HALF DUPLEX. Besides establishing the need to echo, UT20 uses this input to calculate the timing parameters necessary to run the terminal. Thus, a single program can operate with wide variations in clock speed or terminal speed.

When UT20 is ready to accept a command, it types out an asterisk (\*) as a prompt character.

#### **?M Commands**

To interrogate memory, type a command such as

#### ?M2F53(CR)

UT20 responds by printing out the contents of memory beginning at location 02F5: three bytes are printed out as two hex digits each. Each line of output begins with the address, and data is grouped in 2-byte (4-digit) blocks. When necessary, new lines are begun

every 16 bytes, with the previous lines ending in semicolons. The user may enter any number of digits to specify the beginning location (leading zeroes are implied, if necessary). If more than four digits are entered, only the last four are used. The number of bytes to be typed out should be in hex. Again, if more than four digits are entered, only the last four are used. This feature allows the correction of a mistake simply by continuing the type and terminating the typed sequence with the correct 4-digit values (230024 is, effectively, 0024). If the number of bytes to be typed is not specified, one byte is assumed. For example:

#### ?M2F5(CR)

would result in the typeout of the one byte at location 02F5.

When the user wants to punch a reloadable paper tape, he requests a memory type-out as previously described.

#### **!M Commands**

In general, data is entered into memory, by means of a command such as

#### !M12F 434F534D4143(CR)

This command enters six bytes (two hex digits each) into memory beginning at location 012F. Once again, the starting location is determined by the last four digits entered. Data is entered into memory after each two hex digits are typed. If the user types an odd number of digits, the last digit is ignored, and the error message ('?') is typed out. It is therefore only necessary to re-enter the last byte.

The !M command provides two options that facilitate memory loading. First, a string of data can be extended from line to line by typing in a comma just before the normal CR. (In this case press the CR-LF (carriage return-line feed) keys before beginning a new line.) For example,

#### !M23 56789ABC,(CR) (LF) DEF0123456,(CR) (LF) 3047(CR)

enters 11 successive bytes beginning at location 0023. Between successive hex pairs while data is being entered, any non-hex character except the comma (and semicolon, as will be discussed) is ignored. This arrangement permits arbitrary LF's, spaces (for readability), nulls (generated by the utility program or by a time-share system to give the carriage time to return), etc.

As a second optional form of data entry, a string of input data can be terminated by a semicolon (and a CR). The utility program then expects more data to follow on the next line, but preceded by a new beginning address. The line must have the format of an !M command, but with the !M omitted. This option provides the mechanism for reading in a paper tape previously punched out as a result of the ?M command. (Recall the format of multiline ?M outputs discussed above.)

The utility program ignores all non-hex characters following !M, allowing CR, LF, and nulls to be inserted in the tape without disturbing the !M command. The semicolon feature allows non-contiguous memory areas to be loaded.

#### **\$U Commands**

The \$U command is used to start program execution. For example,

#### \$U6C(CR)

starts program execution at location 006C with P=X=0. This command will leave the terminal interface and floppy disk interface (if installed) active. Consequently, the user program should not use I/O commands associated with these interfaces. For a further discussion of the terminal interface and the floppy disk interface, see the material on Module Description and Signal Mnemonics in the next Section. For further details on the \$U command, refer to "Two-Level I/O" under Input/Output Interfacing in the next Section.

If only \$U(CR) is typed with no address specified, execution will start at location 0000. If more than 4 address digits are typed, only the last 4 will be used.

#### **\$P Commands**

The \$P command is similar to the \$U command. For example:

#### \$P6C(CR)

would also start program execution at location 006C with P=X=0 except, in this case, the terminal and floppy disk interfaces may be disabled. This feature is a convenience for the user so that his program can use I/O commands normally associated with these peripherals.

If no address is specified, program execution starts from location 0000. The function is equivalent to pushing the RESET then RUN P buttons on the control panel. This command also obeys the 'last-4-digits' address rule.

For further details of this command, refer to "Two-Level I/O" under Input/Output Interfacing in the next Section.

#### **\$L Commands**

The \$L command is used in systems having a floppy disk. Typing

L

causes UT20 to type

READ?

asking for the unit and track number of the diskette file to be loaded. For a discussion of the disk loader program, refer to the RCA COSMAC Floppy Disk System II CDP18S805 Instruction Manual MPM-217. If a floppy disk system is not installed and this command is accidentally activated, simply do a CR after the READ? interrogation, UT20 will type

#### DRIVE NOT ON

and issue an \*, waiting for another command.

#### ?R Commands

When UT20 is activated (via RESET, RUN U), one of the first things it does is save 13-1/2 of the 16 'R' registers of the CPU in its RAM stack located at address 8C00 for 32 bytes. Registers R0, R1, and R4.1 are altered, but the states of the remaining registers are preserved at the time when UT20 was activated. This feature provides a means of examining most CPU registers for debugging purposes.

The ?R command provides for automatic readback of the stored register states with X's for registers R0, R1, and R4.1 to indicate that they have not been preserved. For example, RESET, RUN U, CR then ?R gives this format:

NOTE: the ?R must be the first command given to UT20 after it is started, because UT20 uses the stack itself when other commands are issued. Thus, it may overwrite the preserved registers when executing any command other than ?R.

# Summary of UT20 Operating Instructions

In summary, after receiving the prompt character '\*' the user may type

?M(address) △ (optional count) (CR)

$!M(address) \triangle(data) (Optional, or;) (CR)$

(where the data may have non-hex digits between each hex pair)

\$P (optional address) (CR) \$U (optional address) (CR) \$L ?R (CR)

UT20 ignores initial characters until it detects?,!, or \$. Then inputs which are not compatible with the above formats cause an error message (?).

A further detailed summary of these basic operating instructions is given below, repeating the information just given in a more concise form.

- 1. After pressing "RUN U", the user should press CR (for full-duplex operation). This instruction sets up the bit-serial timing and specifies echo or not.

- 2. UT20 will return \* as a prompt.

- 3. Following \*, UT20 ignores all characters until one of ?, \$, or ! is typed in.

- 4. Following 'M or !M, UT20 waits for a hex character. It then assembles an address. If more than four hex digits are typed, only the last four are used. Next, a space is required. Note:  $\triangle$  denotes a space.'

- a. For ?M addr  $\triangle$  a hex count may follow (again, only the last four digits are kept), and the command is terminated by CR. If no count is entered, one byte will be typed.

- b. For !M addr \( \triangle \) data must follow. An even number of hex digits is required. Before each hex pair arbitrary filler, except for a CR, comma, or semicolon, is allowed. CR terminates the command, unless it is immediately preceded by a comma or, as is generally the case, by a semicolon.

- i. In case of comma CR the user must insert an LF for UT20 to continue to accept data. This procedure is a form of line continuation.

- ii. In case of a semicolon all following characters are ignored until the CR is typed. Then, the user must again provide an LF, and UT20 continues as if it had received optional filler, then a starting address, then a space, and then data.

- iii. The !M command can be followed by as many continuation lines as needed, mixed between the two types if desired, and is finally terminated with a CR not preceded by a comma or semicolon.

- 5. Commands \$P or \$U may be followed by a starting address. The last 4 digits are used if more than 4 are typed in. If no address is given, 0 is assumed. Program execution begins at the specified location with R0 as the program counter •. The \$P command disables the terminal and floppy disk interfaces whereas \$U does not.

- 6. Command \$L starts the floppy disk loader program which will issue the prompt

#### READ?

A proper response is a 4-digit number requesting unit and track number, followed by a CR. If an error is detected during the read operation, a diagnostic message is printed.

- 7. Command 'R causes a readout of the 16 R registers saved when UT20 is initialized. X's are written for those registers not preserved.

- \$P and \$U always begin with R0 as program counter. This arrangement is consistent with the fact that P=0 and X=0 after the CPU is RESET. Refer to the CDP1802 data sheet for other actions of RESET.

- 8. When a !M, ?M or ?R command is accepted and completed, UT20 types another \* prompt.

- 9. When UT20 detects bad syntax, it types out a? and returns the carriage. If a mistake is made when data is entered (by typing in an odd number of digits), all data will have been entered except the last hex digit. Note that the "only-last-four-digits" rule in the address field allows the user to correct an address error without retyping the whole command. For example, a mistaken 234 can be corrected by continuing. Thus, 2340235 is, effectively, 0235. A bad command can be aborted by typing in any illegal character except after !M or "?M or between input hex data pairs. In these cases, the user should type any digit and then, for example, a period.

## **Terminal Interfacing**

#### **ASCII Coding**

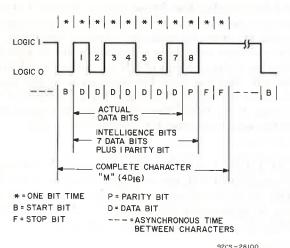

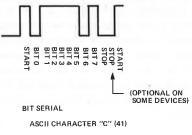

The CDS is designed to interface to a data terminal via a serial ASCII code using either a 20-mA current loop or an EIA RS232C standard electrical interface. When a key is struck on a TTY terminal, the information denoting that character is converted to its ASCII code and appears on the output terminals as a serial data-bit stream. The serial data originating at the TTY for the letter 'M' is shown in Fig. 2. The character is framed by a start bit B and

Fig. 2 — Data terminal bit serial output for the character "M".

two stop bits FF. By convention two stop bits are used for data transmission at 10 characters per second although 1, 1½, or 2 are also acceptable outputs from various different terminals. A parity bit P is also shown. For even parity, the parity bit would be a '1' only if the 7 data bits contain an odd number of '1's.

Hence, the total number of 1's in the eight intelligence bits is always an even number. Some data terminals may be set up to generate either even or odd parity. UT20 ignores the parity bit, so either even or odd parity is acceptable.

Data from the CDS is generated with the same format; i.e., a start bit, 7 data bits, a parity bit, and two stop bits. Note that the CDS does not generate parity - the parity bit is always a '1' regardless of the data bits. Therefore, terminals interfacing to the CDS should ignore the parity bit.

#### **UT20 Read and Type Routines**

The UT20 read and type routines provide the basic software mechanism for communication between the CDS and data terminal. Several different routines are available to facilitate different types of I/O data transfers.

These routines are designed to allow adoption to various terminal speeds and to determine whether or not characters read in should be "echoed" (ie., typed back immediately). For these purposes, a 'subsubroutine' called DELAY is included which provides the necessary bit timing delays to the read and type routines. DELAY uses RC as its program counter, which must be set-up to point to location 80EF. UT20 does this automatically when it is started. Any user program using a read or type routine must not alter RC, or must restore it to 80EF before calling a read or type routine. Also, the upper half of register RE (RE.1) contains a control constant. The least significant bit specifies echo (0 denotes echo, I denotes no echo). For full-duplex operation, then, this bit is a zero. Again, this is automatically set when UT20 is started and the CR or LF characters received.

The remainder of RE.1 constitutes a timing parameter (TP). TP is calculated as follows:

TP = 2 x

$$\frac{\text{interval between two serial bits}}{320 \text{ x (CPU clock period)}}$$

where the fraction is rounded to the nearest integer. For example, because a Teletype Model 33 operates at 10 characters per second and 11 bits per character, for the CDS running from the supplied 2.0-MHz clock,

The factor of 2 comes from the fact that the input serial waveform is sampled over two successive bit times. The factor of 320 comes from the fact that the time between samples is 20 instruction times, with each instruction taking 16 clock periods.

TP = 2 x

$$\frac{\frac{1 \text{ s}}{10 \text{ char}} \times \frac{1 \text{ char}}{11 \text{ bits}}}{\frac{320 \times \frac{1 \text{ s}}{2.0 \times 10^6}}{2.0 \times 10^6}}$$

= 2 x 56.8 (rounded to 57)

= 114<sub>10</sub> = 72<sub>16</sub>

Because for proper operation TP must be less than 255, there is a bound on the speed of terminals supported at any given clock rate. Faster terminals or slower clocks can be supported to the extent that roundoff errors do not cause bad timing. For example, at 2.0 MHz and 30 10-bit characters per second,

TP = 2 x

$$\left[ \frac{\frac{1}{30} \times \frac{1}{10}}{320/2.0 \times 10^6} \right]$$

= 2(20.8) = 42<sub>10</sub> = 2A<sub>16</sub>

and the round-off error is small (2100 instead of 20.8). On the other hand, at 2.0 MHz with baud rates above 1200, the round-off error would be too high.

The utility program UT20 uses a subroutine "TIMALC" to generate the operating time constant, using the first character typed in by a user. This routine times the intervals between incoming bits to calculate TP and reads one bit to determine whether or not to echo. Specifically, if a CR is entered while TIMALC is running, then echoes will be provided; an LF suppresses echoes. In either case, RE.1 is loaded with the appropriate constant. TIMALC also loads the subroutine pointer for the DELAY routine. The user of TYPE and READ has the option of calling TIMALC or setting up RE.1 and the pointer to the DELAY routine himself. As a convenience to the user, UT20 leaves RE.1 and RC properly adjusted while performing a \$P or \$U operation and may be used unless they have been altered by the user.

All read and type routines and TIMALC use R3 as their program counter, and return to the caller with SEP R5. They can be called directly from a program that can use R5 as its program counter, or they may be called through the Standard Call and Return Technique (SCRT) described in the User the **CDP1802** COSMAC Manual for Microprocessor, **MPM-201** in the Section Programming Techniques under "Subroutine Techniques". This programming technique is the most general and is recommended.

RE.1 is reserved for the operating constant (control constant 0 or 1 added to the timing parameter TP) discussed above.

One byte of RAM is needed by read and type routines. These routines assume that R2 points to free RAM and M(R(2)) is altered by them. In general, the user can set R2 to any free RAM location. UT20 uses a byte in its dedicated RAM for this purpose.

RF.1 is used in certain cases to pass the byte being read or typed between the calling routine and these subroutines. When READ is exited, it leaves the input byte in RF.1. When TYPE is entered at location 81A4, the byte to be typed is taken from RF.1.

All routines alter RE.0 and RF.0. They also alter D, DF, and X. The READ routine leaves the input byte in D as well as in RF.1, but the byte in D will be destroyed if the Standard Call and Return Technique is used.

When TIMALC exits, R3.1 is left holding A.1 (READ) = A.1 (TYPE) = 81, but R3.0 is meaningless. When READ exits, R3 is ready for entry at READAH (see Table II). When TYPE exits, R3 is ready for entry at TYPE5 (see same table). When DELAY exits, RC is ready for another call to DELAY. When the Standard Call and Return Technique is used, R3 is automatically set up.

The READ routine has two entry points - READ and READAH. The former acts as described above and has no other side-effects. The latter operates just as READ does, but with the following side-effect. If the character read in is a hex character (0-9, A-F) then the 16-bit contents of RD are shifted four bits to the left, and the 4-bit hex equivalent of the input character is entered at the right. DF is then set to 1 on exiting. If the input character is not a hex character, RD is not affected, but DF is set to 0 on exiting.

CAUTION: A READ may immediately be followed by another READ, but not immediately by a TYPE. The caller should wait 1.5 bit times first, which he can do by entering TYPE at TYPE5D or by calling DELAY, with a parameter of 7 or greater.

The DELAY subroutine assumes that the calling program counter is R3. It uses the value, n, of the immediate byte at M(R3) to generate a delay equal to

$$(20 + m (2n + 6))$$

instruction times

where m is time constant in RE.1 (see previous discussion). It then increments R3 past the calling parameter and returns via a SEP R3.

The TYPE routine has five different entry points. Three of them simply specify different places to fetch the character from: TYPE types from RF.1, TYPE5 types from M(R5) and increments R5, and TYPE6 types from M(R6) and increments R6. TYPE5D is an entry which provides a 1.5-bit delay before going to TYPE5. The purpose of this delay is to let an immediately preceding echoed READ process to completion before typing. TYPE2 is an entry which results in RF.1 being typed out in hex form as two hex digits. Each 4-bit half is converted to a ASCII hex digit (0-9, A-F) and separately typed out.

Notice that the READ routines are designed to facilitate repeated calls on READAH, while the TYPE routines are designed for repeated calls to TYPE5. In order to output a string of variable data characters following a READ, given the timing restriction mentioned earlier, it is most logical to call TYPE5D first, using an immediate "punctuation"

byte (i.e., non-data such as space, null, etc.) to get the required initial delay and to follow either with repeated calls on TYPE (with the output variable data characters picked up from RF.1) or repeated calls on TYPE5 using immediate data characters. This procedure permits a maximum output character rate.

Another routine, OSTRNG, can be used to output a string of characters. OSTRNG picks up the character string pointed to by R6 and tests each character for zero. The characters should be already encoded in ASCII. If a zero is found (ASCII 'null'), the program terminates and returns control to the user via a SEP R5. If the character is not a zero, it is typed out to the terminal. The OSTRNG routine includes a delay on the front end so that it may be called at any time - even following a read.

Tables I and II summarize the functions and calling sequences just described.

TABLE I – UT20 REGISTER UTILIZATION

| Register<br>Name | Register<br>Number | Function and Comments                                                        |

|------------------|--------------------|------------------------------------------------------------------------------|

| PTER<br>CL       | R0 }               | Altered by UT20 while storing registers. R4.1 is similarly altered.          |

| ST               | R2                 | Pointer to RAM "work" byte. UT20 uses R2 = 8C00.                             |

| SUB              | R3                 | Program counter for all routines except DELAY.                               |

| PC               | R5                 | Program counter for UT20 which calls the routines above.                     |

| DELAY            | RC                 | Program counter for the DELAY routine. Points to DELAY1 in memory.           |

| ASL              | RD                 | Assembled into by READAH (input hex digits).                                 |

| AUX              | RE                 | RE.1 holds time constant and echo bit.                                       |

|                  |                    | RE.0 is used by all READ and TYPE routines and by TIMALC, OSTRNG, and CKHEX. |

| CHAR             | RF                 | RF.1 holds input/output ASCII character.                                     |

|                  |                    | RF.0 is used by all READ and TYPE routines and by TIMALC, OSTRNG, and CKHEX. |

TABLE II - UT20 READ AND TYPE CALLING SEQUENCE

| Entry<br>Name                     | Absolute<br>Address          |                                                                                                                                                                                               |

|-----------------------------------|------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| READ<br>READAH<br>TYPE5D<br>TYPE5 | 813E<br>813B<br>819C<br>81A0 | Input ASCII → RF.1, D (if non-standard linkage) Same as READ. If hex character, DIGIT → RD (see text) 1.5-bit delay. Then TYPE5 function. Output ASCII character at M(R5). Then increment R5. |

| TYPE6<br>TYPE                     | 81A2<br>81A4                 | Output ASCII character at M(R6). Then increment R6. Output ASCII character at RF.1.                                                                                                           |

| TYPE2<br>TIMALC                   | 81AE<br>80FE                 | Output hex digit pair in RF.1. Read input character and set up control byte in RE.1.                                                                                                          |

| DELAY1<br>OSTRNG                  | 80EF<br>83F0                 | Initialize RC to point to DELAY1.  Delay, as function of M(R3) (see text). Then R3 + 1.  Output ASCII string at M(R6). Data byte 00 ends typeout.                                             |

#### Notes

- All routines, except DELAY, use R3 as program counter, exit with SEP5, and alter registers X, D, DF, RE, RF and location M(R2).

- (2) DELAY routine uses RC as program counter.

- exits with SEP3 after incrementing R3, and alters registers X, D, DF, and RE.

- (3) READ and READAH exit with R3 pointing back at READAH.

- (4) All five TYPE routines exit with R3 pointing at TYPE5.

# Examples of UT20 Read and Type Usage

The following examples should help clarify how to use the UT20 read and type subroutines. Most examples use the standard subroutine linkage which requires that R2 point at a free RAM location.

#### **Read Routines**

This sample program will read four ASCII hex characters into register RD translating them from ASCII to hex in the process. Reading will terminate when a carriage return is entered. Entry of a non-hex digit other than a carriage return will cause a branch to an error program which will type out a "?". This sample program uses the standard subroutine call and return linkage.

#### READAH=#813B

LOOP: SEP R4,A(READAH) .. Call the hex .. read program BDF LOOP .. As long as ASCII hex .. digits are entered .. Read and shift in .. Fall through if not hex .. character GHI RF .. See what character was last .. entered XRI#0D .. Was it carriage return BNZ ERROR ...If not, BR to error .. Characters entered are now .. in RD

The READ routine (at 813E) could be used similarly to enter characters; however, READ only enters them one at a time into RF.1 (and D) writing over the previous entry. Note that, even though incoming data is entered into D, the subroutine return program alters D. Therefore, valid data will only be found in RF.1 (and RD when READAH is used) if the standard subroutine call and return programs are used. An alternative technique is to use R5 as the main program counter (since all read and type routines terminate with a SEP R5) and call the program with a SEP R3 (since all read and type routines use R3 as their program counter). The following example illustrates this technique.

#### **Type Routines**

**EXAMPLE 1:** This program outputs a single character using the TYPE5 routine. It uses R5 as the program counter.

...Set R3 to TYPE5 routine LDI#81 PHIR3 LDI#A0 PLOR3 LDI #FF ..Set R2 to free RAM location #3FFF PLO<sub>R2</sub> LDI#3F PHIR2 SEP R3 ...Call type ,T'R' ...An "R" will be typed ...Next instruction уу

The TYPE5D routine is used in the same way.

EXAMPLE 2: This program outputs a character using the TYPE6 routine. Note that R6 should be the program counter for the program calling TYPE6 if the character to be typed is an immediate byte because TYPE6 must always be from M(R6). But, because TYPE6 exits with SEP 5, TYPE6 must always be called using standard subroutine linkage for typing an immediate byte. An alternative is to use R5 as the main program counter but point R6 at the memory location containing the byte to be typed. This example uses standard subroutine linkage.

SEP R4 ...Branch to the call routine ,#81A2 ...Address of TYPE6 ,T'?' ...Byte to be typed out ...Next instruction

**EXAMPLE 3:** The TYPE and TYPE2 routines pick up the byte in RF.1 for typing. TYPE simply outputs the character, whereas TYPE2 considers RF.1 a hex digit pair which it encodes in ASCII before typing. This example types out the hex digits 'D5', and uses standard subroutine linkage.

LDI #D5 ...Load hex digits D5

PHI RF ...Into RF.1

SEP 4 ...Call TYPE2

,#81AE

yy ...Next instruction

Note that all type routines, except TYPE2, expect the character they pick up to be already encoded in ASCII.

EXAMPLE 4: An entire message can be typed by using the OSTRNG routine. The ASCII bytes pointed to by R6 will be typed. When a '00' byte is detected, OSTRNG returns to the caller. This example will output the string

RCA COSMAC MICROPROCESSOR

The standard call and return linkage is assumed.

OSTRNG = #83F0

SEP R4,A(OSTRNG) ...Call OSTRNG

DC T'RCA COSMAC' ...1st Line

,#0D0A ...(CR) (LF)

,T'MICROPROCESSOR'..2nd Line

,#00 ...End of Text

# Additional Utility Routines

#### ASCII to Hex Conversion Routine

The ASCII to hex conversion, CKHEX, examines the ASCII character in RF.1. If this character is not a hex digit, CKHEX returns to the user (via SEP R5) with DF = 0. If the character is hex, CKHEX returns with RE.0 = hex digit, DF = 1 and with the digit shifted into the least significant 4 bits of register RD. CKHEX uses the registers described above and, as with the other routines, is most readily handled via the standard call and return techniques. CKHEX is located at 83FC.

#### **Initialization Routines**

Two routines are provided, INIT1 and INIT2, which initialize CPU registers for the standard call and return technique. These routines set up registers as follows:

| R2 = R(X) | - pointing to the last (highest) available user RAM location |

|-----------|--------------------------------------------------------------|

|           | (below 8000).                                                |

| R3 + =    | - will become the program counter                            |

|           | on return                                                    |

| R4        | - pointing to the call routine in                            |

|           | UT20                                                         |

| R5        | - pointing to the return routine in                          |

|           | UT20                                                         |

The INIT programs examine user memory area (below address 8000) and determine how much memory is present. They set R2 to the highest available RAM address, which is 03FF for the CDS as supplied (with one 4-kilobyte RAM card).

The only difference between INIT1 and INIT2 is the location to which they return. INIT1 returns to location 0005 with P = 3, while INIT2 simply returns by setting P = 3 and assumes that the user has already set R3 pointing to the correct return point. These programs are intended as a convenience to free the user from generating the overhead code required by the standard subroutine technique. They may also be used as an integral part of custom support programs running on the CDS. Their absolute addresses are INIT1 = 83F3 and INIT2 = 83F6. Refer to Appendix G, the UT20 listing, for the absolute addresses of CALL and RET, which will be loaded into R4 and R5 respectively.

Following are examples of the use of these programs:

#### EXAMPLE 1: Using INIT1 INIT1 = #83F3

#### **Address Code Mnemonics Comment**

| 0000 | 71         | DIS,#00   | Disable interrupts              |

|------|------------|-----------|---------------------------------|

| 0001 | 00         |           |                                 |

| 0002 | C0         | LBR INIT1 | Initialize registers            |

| 0003 | 83         |           |                                 |

| 0004 | <b>F</b> 3 |           |                                 |

| 0005 |            | USRPGM:   | User program starts here;       |

|      |            |           | $\mathbf{p} = \hat{\mathbf{p}}$ |

#### EXAMPLE 2: Using INIT2 INIT2 = #83F6

#### **Address Code Mnemonics Comment**

| 0000 | 7.1           | DIS,#00   | Disable interrupts  |

|------|---------------|-----------|---------------------|

| 0001 | 00            |           | ·                   |

| 0002 | F8            | LDI A.1   | Set R3 to return    |

|      |               | (START)   |                     |

| 0003 | 00            | ,         | point               |

| 0004 | <b>B</b> 3    | PHI R3    |                     |

| 0005 | F8            | LDI A.0   |                     |

|      |               | (START)   |                     |

| 0006 | 50            |           |                     |

| 0007 | $\mathbf{A}3$ | PLO R3    |                     |

| 8000 | C0            | LBR INIT2 | Call INIT2          |

| 0009 | 83            |           |                     |

| 000A | F6            |           |                     |

|      |               |           |                     |

|      | 0             |           |                     |

| 0050 |               | START:    | User program starts |

here

#### **Routine to Restart UT20**

A means is provided to automatically transfer control back to UT20 from a user program. An entry point routine, GOUT20, is provided for this purpose. When entered via this routine, UT20 will restart and issue a \* prompt to the terminal. A long branch to GOUT20 at location #83F9 will cause this transfer. UT20 depends on the following conditions upon reentry:

1) RE.1 = terminal timing constant 2) Two-level I/O is enabled

In order to assure the second condition, the user program must be initiated via the \$U command. The GOUT20 routine can be called only by a program having R3 as its program counter.

### **Additional Notes on UT20**

UT20 automatically enables group 1 I/O devices,

which includes the terminal and floppy disk interfaces, when it is started. User-added I/O devices wired to the same group-select signal are also enabled. For more information on this subject, refer to "Two-Level I/O" under Input/Output Interfacing in the next Section, titled Hardware Structure of the CDS.

Interrupts are automatically disabled when UT20 is running. They are re-enabled by either the \$P or \$U command. Because R1 and R2 must be initialized by a user program before interrupts are allowed, UT20 prohibits start-up via these commands if an Interrupt is pending. Instead, it will type INTERRUPT and issue an \*. This feature is a convenience to the user to prevent start-up problems if interrupts have not been externally disabled. If custom hardware is installed that may cause interrupts at start-up, the user program should be started via the RUN P switch.

# **Programming Methods**

## Machine Language Programming

With an understanding of the structure and operation of the CPU and the material provided thus far, the reader is prepared to begin using the Development System in an elementary way. For example, he can now understand and possibly modify the time-out test program presented earlier in this Manual. However, almost any hexadecimal (machine language) test program will require use of the I/O typewriter. The most basic way to communicate by the teletypewriter, therefore, will be covered next.

To read a character from the I/O teletypewriter, the user program should transfer control to READ (in UT20). That is, load R3 with 813E and execute a D3 instruction, making sure that R2 is pointing to a free RAM location. After the typed character is read, the utility routine will return by setting P to 5, i.e., by executing the instruction D5 (making it most convenient if the program counter of the calling routine were 5 to begin with). The ASCII code for the input character (with a 0 parity bit) will be in both RF.1 and in D. The memory location pointed to by R2 and registers RE, RF, X, and DF will have been changed in value (not preserved over the call).

A list of key UT20 symbolic locations and their corresponding absolute memory addresses is given in Table II. Because the READ routine uses R3 as its program counter, it is most convenient to branch to READ by a D3 instruction. When READ returns to the caller, R3.0 will contain a modified value, necessitating another initialization if a repeated I/O is to be performed. Because the READ routine uses the values in registers RC and RE which UT20 will normally initialize, it is essential that the user refrain from using these registers unless their values are saved and later restored by his program.

To cause a character to be typed out by the I/O typewriter, the user program should transfer control to TYPE5D at location 819C, by means of a D3 instruction, again making sure that R2 is pointing to a free RAM location. As discussed above, the calling P value should be 5 and, for this case, the ASCII code for the output character should be an immediate byte (i.e., the byte after the D3 instruction). After typing the character, READ will have advance R5 past the argument byte and again return by a D5 execution. M(R(2)), as well as registers RE, RF, X, D, DF, and R3.0 return altered. All other register values are preserved. For the reasons previously cited, the user should again refrain from using registers RC and RE.

Given the ability to execute simple I/O terminal functions, the user can now code elementary test programs to further exercise the COSMAC Development System. As a simple example, consider the routine shown in Fig. 3 that reads two bytes, compares them, and outputs the "larger" of the two.

| counter. |  |  |

|----------|--|--|

|          |  |  |

|          |  |  |

|          |  |  |

| unter.   |  |  |

| 7        |  |  |

|          |  |  |

|          |  |  |

|          |  |  |

|          |  |  |

|          |  |  |

|          |  |  |

| ond.     |  |  |

|          |  |  |

|          |  |  |

|          |  |  |

|          |  |  |

|          |  |  |

|          |  |  |

|          |  |  |

Fig. 3 - Example of elementary hexadecimal program.

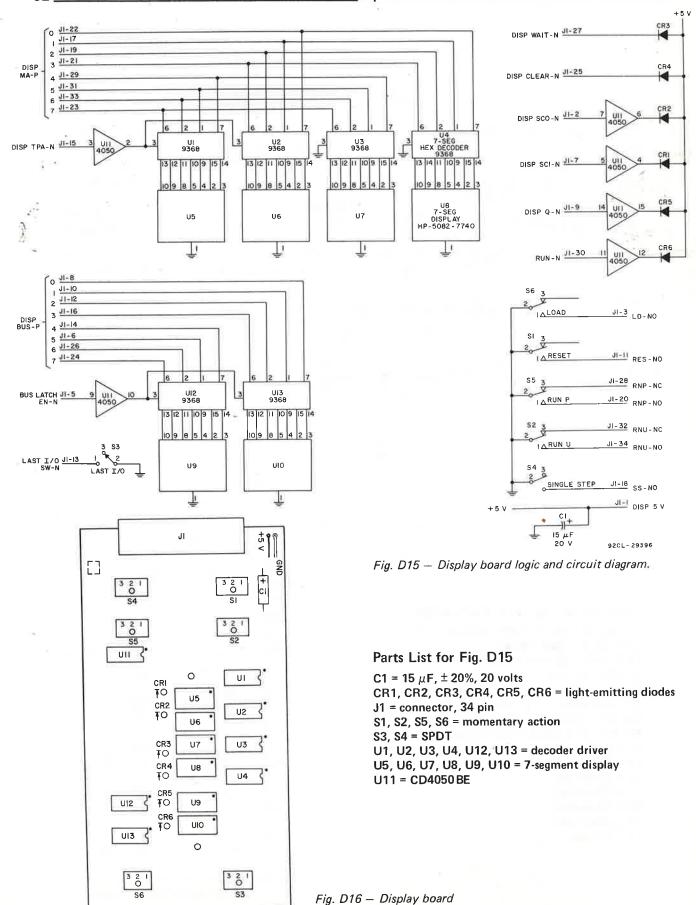

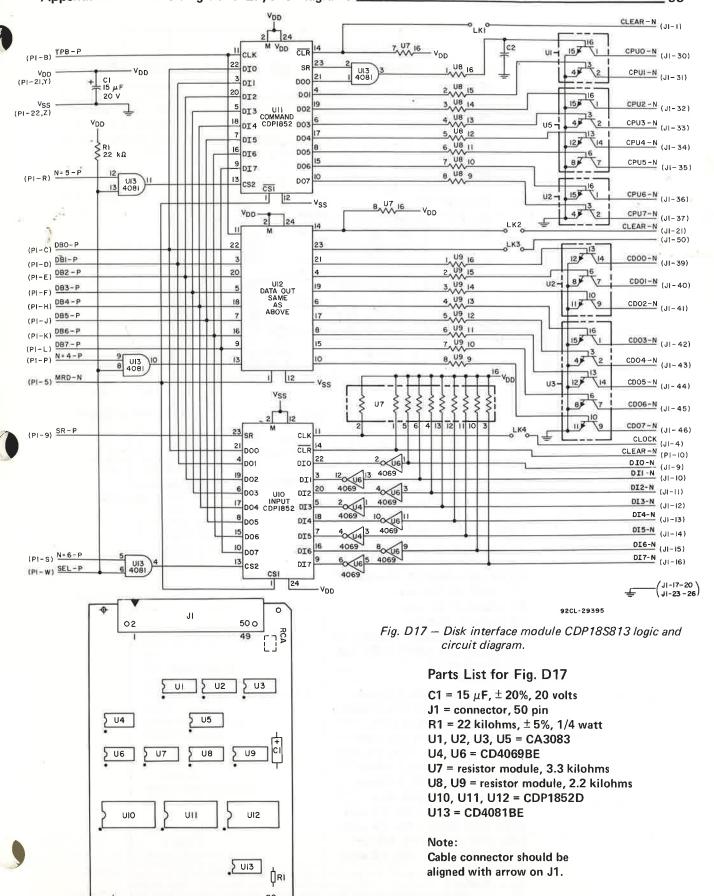

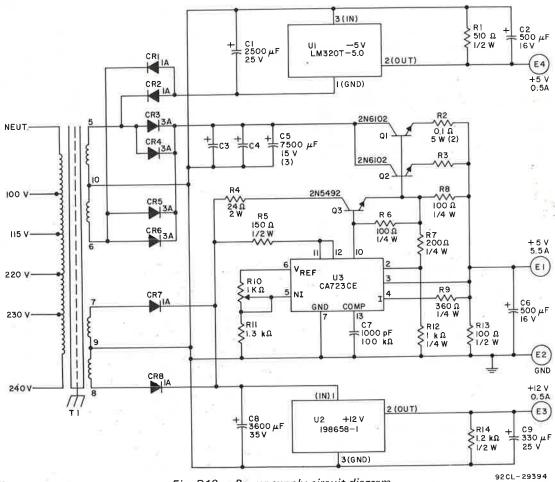

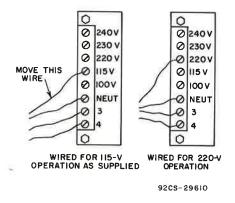

The routine given exhibits register usage compatible with the UT20 READ and TYPE calling sequences. Further, the I/O instructions consist of calls to the appropriate teletypewriter interface routines.